# University of Nebraska - Lincoln Digital Commons @ University of Nebraska - Lincoln

Computer Science and Engineering: Theses, Dissertations, and Student Research

Computer Science and Engineering, Department of

Fall 2012

# Improving Performance of Solid State Drives in Enterprise Environment

Jian Hu

University of Nebraska-Lincoln, jhu@cse.unl.edu

Follow this and additional works at: http://digitalcommons.unl.edu/computerscidiss

Part of the Computer Engineering Commons, and the Computer Sciences Commons

Hu, Jian, "Improving Performance of Solid State Drives in Enterprise Environment" (2012). Computer Science and Engineering: Theses, Dissertations, and Student Research. 47.

http://digitalcommons.unl.edu/computerscidiss/47

This Article is brought to you for free and open access by the Computer Science and Engineering, Department of at DigitalCommons@University of Nebraska - Lincoln. It has been accepted for inclusion in Computer Science and Engineering: Theses, Dissertations, and Student Research by an authorized administrator of DigitalCommons@University of Nebraska - Lincoln.

# IMPROVING PERFORMANCE OF SOLID STATE DRIVES IN ENTERPRISE ENVIRONMENT

by

Jian Hu

#### A DISSERTATION

Presented to the Faculty of

The Graduate College at the University of Nebraska

In Partial Fulfilment of Requirements

For the Degree of Doctor of Philosophy

Major: Engineering

Under the Supervision of Professor Hong Jiang

Lincoln, Nebraska

December, 2012

IMPROVING PERFORMANCE OF SOLID STATE DRIVES IN ENTERPRISE

ENVIRONMENT

Jian Hu, Ph. D.

University of Nebraska, 2012

Adviser: Hong Jiang

Flash memory, in the form of Solid State Drive (SSD), is being increasingly employed in mobile and enterprise-level storage systems due to its superior features such as high energy efficiency, high random read performance and small form factor. However, SSD suffers from the *erase-before-write* and endurance problems, which limit the direct deployment of SSD in enterprise environment. Existing studies either develop SSD-friendly on-board buffer management algorithms, or design sophisticated Flash Translation Layers (FTL) to ease the erase-before-write problem. This dissertation addresses the two issues and consists of two parts.

The first part focuses on the white-box approaches that optimize the internal design of SSD. We design a write buffer management algorithm on top of the logblock FTL, which not only optimizes the write buffer effect by exploiting both the recency and frequency of blocks in the write buffer, but also minimizes the destaging overhead by maximizing the number of valid pages of the destaged block. We further identify that the low garbage collection efficiency problem has a significantly negative impact to the performance of the page-mapped SSD. We design a GC-Aware RAM management algorithm that improves the GC efficiency even if the workloads do not have updating requests by dynamically evaluating the benefits of different destaging policies and adaptively adopting the best one. Moreover, this algorithm minimizes the

address translation overhead by exploiting the interplay between the buffer component and the FTL component.

The second part focuses on the black-box approaches that optimize the SSD performance externally. As an increasing number of applications deploy SSD in enterprise environment, understanding the performance characteristics of SSD in enterprise environment is becoming critically important. We identify several performance anomalies of SSDs and their performance and endurance impacts on SSD employed in enterprise environment by evaluating several commercial SSDs. Our study provides insights and suggestions to both system developers and SSD vendors. Further, based on the performance anomalies identified, we design an IO scheduler that takes advantage of the SSD features and evaluate its performance on SSD. The scheduler is shown to improve performance in terms of bandwidth and average response time.

#### ACKNOWLEDGMENTS

First of all, I would like to express my thanks to my advisor, Dr. Hong Jiang, for his support, guidance and encouragement during my five-year Ph.D. study at University of Nebraska-Lincoln. Dr. Jiang not only teaches me how to do research, but also teaches me how to improve my writing skills and presentations. Without his patient advise and input, this dissertation would never have been possible. The training I get here from Dr. Jiang will help my future career development significantly. It has been a great honor for me to do research under Dr. Jiang's supervision.

I would also like to express my thanks to my advisory committee members Dr. Lisong Xu, Dr. Witawas Srisa-an and Dr. Song Ci for their very helpful input during my study. Their valuable advise and support have played an important role in my completing my Ph.D. study.

I'm particularly grateful to Lei Tian and Bo Mao for their input and discussions on my research. They are always ready when I have questions that I can not solve on my own. Without their patient help and time, my research would not have gone so smoothly.

I also would like to thank all members of the ADSL group. These people include Lei Xu, Hao Luo, Dongyuan Zhan, Ziling Huang, Yaodong Yang, Junjie Qian and Stephen Mkandawire. They are very helpful in our group meetings and discussions. I feel very glad to work with them in the ADSL group for the past five years.

I thank my parents for their support and love. They always encourage me when I feel discouraged and want to give up.

Most of all, I must thank my wife, Chijun Deng, for her endless love and encouragement. During the past five years, Chijun sacrificed a lot of her time to help me study and research. Without her, I would never have finished my dissertation.

## Contents

| C  | onter | $\operatorname{nts}$ |                                                   | V    |

|----|-------|----------------------|---------------------------------------------------|------|

| Li | st of | Figure               | es                                                | X    |

| Li | st of | Tables               | 5                                                 | xiii |

| 1  | Intr  | oducti               | ion                                               | 1    |

|    | 1.1   | NANI                 | O flash memory SSD characteristics                | 1    |

|    |       | 1.1.1                | Characteristics                                   | 1    |

|    |       | 1.1.2                | Two physical limitations of SSD                   | 2    |

|    | 1.2   | SSD fu               | unctional components                              | 3    |

|    |       | 1.2.1                | Flash translation layer (FTL)                     | 5    |

|    |       | 1.2.2                | SSD-friendly write buffer                         | 8    |

|    | 1.3   | The S                | SD design space and the scope of the dissertation | 10   |

|    |       | 1.3.1                | White-box approaches                              | 10   |

|    |       | 1.3.2                | Black-box approaches                              | 12   |

|    | 1.4   | Contri               | butions of the dissertation                       | 13   |

|    | 1.5   | Disser               | tation Organization                               | 16   |

| 2 | Design and Implementation of a Write Buffer Management Algo- |        |                                                              |    |  |  |

|---|--------------------------------------------------------------|--------|--------------------------------------------------------------|----|--|--|

|   | $\operatorname{rith}$                                        | m of S | SSD                                                          | 17 |  |  |

|   | 2.1                                                          | Backg  | round                                                        | 18 |  |  |

|   | 2.2                                                          | Design | and implementation                                           | 22 |  |  |

|   |                                                              | 2.2.1  | Predicted Average Update Distance                            | 23 |  |  |

|   |                                                              | 2.2.2  | Destaging Efficiency                                         | 25 |  |  |

|   |                                                              | 2.2.3  | Implementation of PUD-LRU                                    | 27 |  |  |

|   |                                                              | 2.2.4  | Data integrity concern                                       | 30 |  |  |

|   | 2.3                                                          | Perfor | mance evaluation                                             | 30 |  |  |

|   |                                                              | 2.3.1  | Experimental setup                                           | 30 |  |  |

|   |                                                              | 2.3.2  | Number of erasures and average response time                 | 3  |  |  |

|   |                                                              | 2.3.3  | Sensitivity study                                            | 35 |  |  |

|   |                                                              | 2.3.4  | Destaging efficiency                                         | 37 |  |  |

|   |                                                              | 2.3.5  | Summary                                                      | 39 |  |  |

| 3 | Des                                                          | ign an | d Implementation of Garbage Collection Efficiency-Aware      |    |  |  |

|   | $\mathbf{R}\mathbf{A}$                                       | M Mai  | nagement                                                     | 41 |  |  |

|   | 3.1                                                          | Backg  | round                                                        | 42 |  |  |

|   |                                                              | 3.1.1  | Performance impact of GC efficiency in SSD                   | 42 |  |  |

|   |                                                              | 3.1.2  | GC-efficiency obliviousness of write-buffer management       | 46 |  |  |

|   |                                                              | 3.1.3  | Partitioning RAM for the write buffer and the mapping table  | 49 |  |  |

|   |                                                              | 3.1.4  | Reducing write-back traffic due to mapping entry replacement | 50 |  |  |

|   | 3.2                                                          | Design | and implementation of GC-ARM                                 | 53 |  |  |

|   |                                                              | 3.2.1  | The design of FTL component                                  | 54 |  |  |

|   |                                                              | 3.2.2  | GC-aware destaging                                           | 56 |  |  |

|   |                                                              | 3.2.3  | Adaptive adjustment of RAM space partitioning                | 58 |  |  |

|   |      |          |                                                                | vii |

|---|------|----------|----------------------------------------------------------------|-----|

|   |      | 3.2.4    | Interplay between write buffer and cached mapping table        | 59  |

|   |      | 3.2.5    | Data integrity concern                                         | 59  |

|   | 3.3  | Perform  | mance evaluation                                               | 60  |

|   |      | 3.3.1    | Experimental setup                                             | 60  |

|   |      | 3.3.2    | Performance and GC efficiency                                  | 60  |

|   |      | 3.3.3    | Write traffic reduction                                        | 69  |

|   | 3.4  | Summ     | ary                                                            | 73  |

| 4 | Ider | ntifying | g Performance Anomalies in Enterprise Environment              | 74  |

|   | 4.1  | Backgr   | round                                                          | 75  |

|   |      | 4.1.1    | Low GC efficiency                                              | 75  |

|   |      | 4.1.2    | Predicting the residual lifetime of SSDs                       | 75  |

|   |      | 4.1.3    | High random read performance                                   | 76  |

|   |      | 4.1.4    | Achieving high bandwidth and low average response time simul-  |     |

|   |      |          | taneously                                                      | 77  |

|   | 4.2  | Experi   | ment                                                           | 77  |

|   |      | 4.2.1    | Experiment setup                                               | 77  |

|   |      |          | 4.2.1.1 Experimental evaluation environment                    | 77  |

|   |      |          | 4.2.1.2 SSD-specific considerations and evaluation methodology | 78  |

|   |      |          | 4.2.1.3 Evaluation tools                                       | 79  |

|   |      |          | 4.2.1.4 Commercial SSD products evaluated                      | 80  |

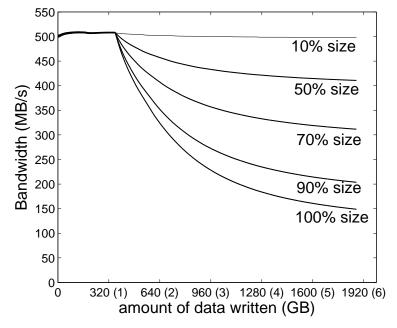

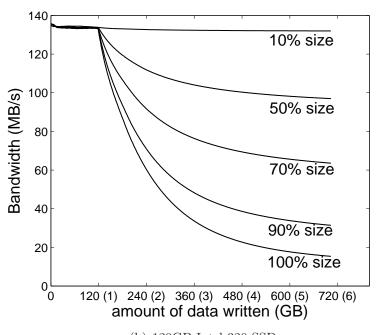

|   |      | 4.2.2    | Performance impact of GC efficiency                            | 82  |

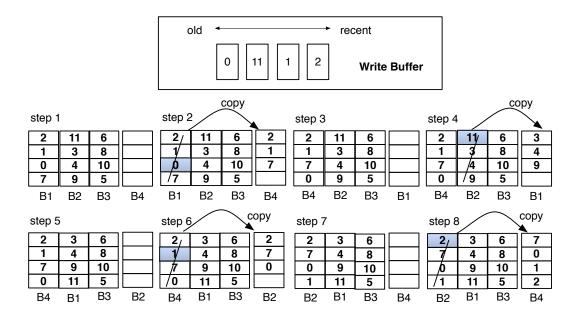

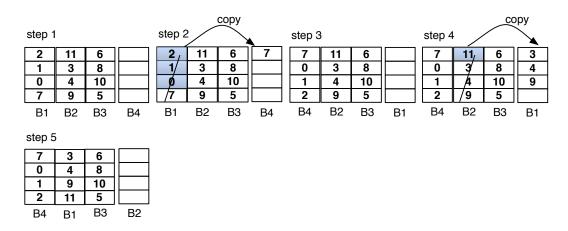

|   |      | 4.2.3    | Performance impact of the mapping policy of FTL                | 87  |

|   |      | 4.2.4    | Predicting the residual lifetime of SSD based on a predefined  |     |

|   |      |          | space allocation scheme                                        | 89  |

4.2.5 Unpredictability of random read performance . . . . . . . . .

|   |     | 4.2.6           | Achieving high bandwidth and low average response time simul- |     |

|---|-----|-----------------|---------------------------------------------------------------|-----|

|   |     |                 | taneously                                                     | 98  |

|   | 4.3 | Guide           | lines and suggestions                                         | 102 |

|   | 4.4 | Summ            | nary                                                          | 105 |

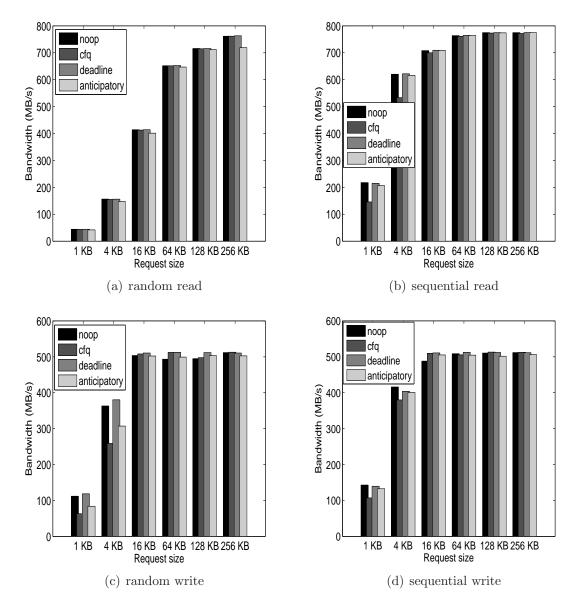

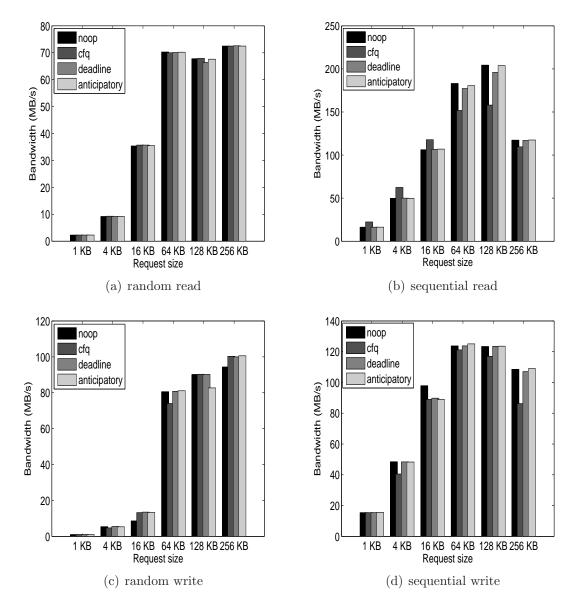

| 5 | SSI | <b>)-F</b> rien | adly IO Scheduling                                            | 107 |

|   | 5.1 | Backg           | round                                                         | 108 |

|   |     | 5.1.1           | IO schedulers and its ineffectiveness to SSD                  | 108 |

|   |     | 5.1.2           | Ineffectiveness of conventional IO schedulers to SSD          | 110 |

|   |     | 5.1.3           | Impact of mixing read and write requests                      | 112 |

|   |     | 5.1.4           | Key factors determining the performance of SSD                | 114 |

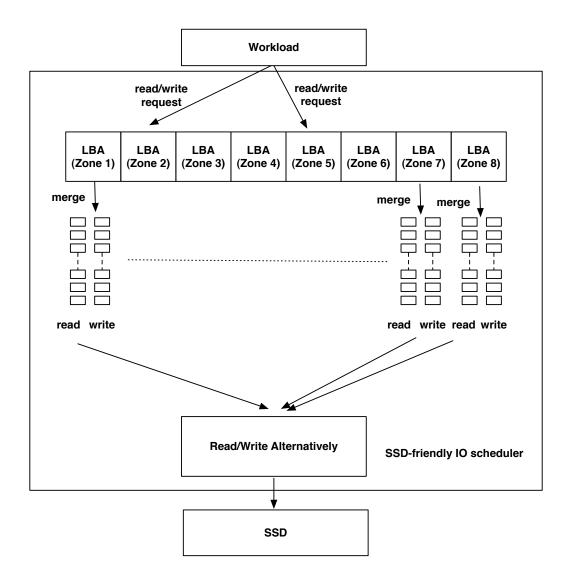

|   | 5.2 | Design          | and implement of SSD-friendly IO scheduler                    | 115 |

|   |     | 5.2.1           | Dividing (logical block address) LBA into zones to maximize   |     |

|   |     |                 | parallelism                                                   | 116 |

|   |     | 5.2.2           | Splitting read and write requests                             | 117 |

|   |     | 5.2.3           | Merging to increase the request size                          | 117 |

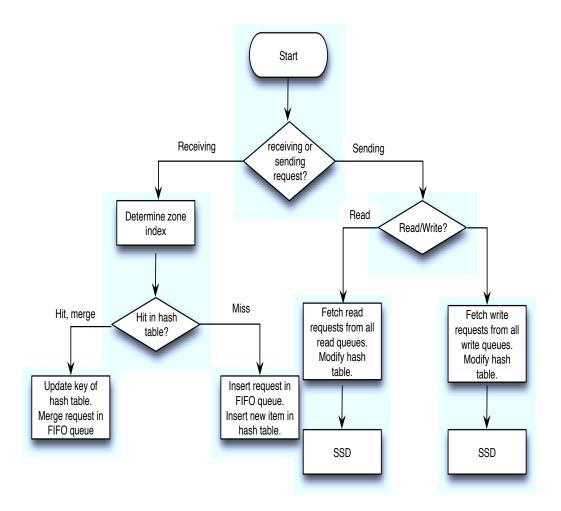

|   |     | 5.2.4           | Flowchart of SSD-friendly IO scheduler                        | 118 |

|   | 5.3 | Perfor          | mance evaluation                                              | 119 |

|   |     | 5.3.1           | Experiment setup                                              | 119 |

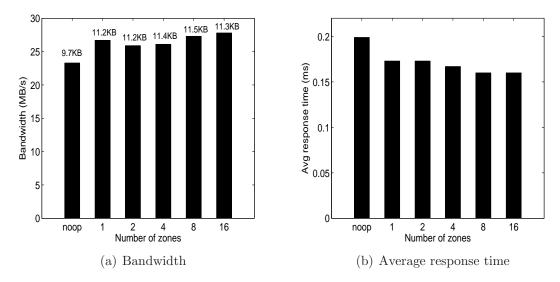

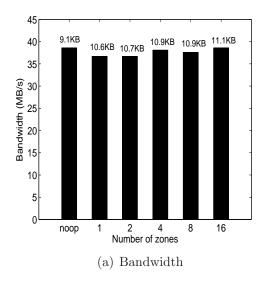

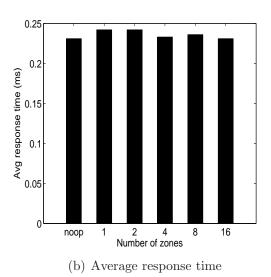

|   |     | 5.3.2           | Result analysis                                               | 120 |

|   | 5.4 | Summ            | nary                                                          | 124 |

| 6 | Rel | ated V          | Vork                                                          | 125 |

|   | 6.1 | NVRA            | AM                                                            | 125 |

|   | 6.2 | Study           | categorization                                                | 126 |

| 7 | Cor | nclusio         | n and Future Work                                             | 128 |

| 7.1 PUD-LRU write buffer management algorithm                            | 128 |

|--------------------------------------------------------------------------|-----|

| 7.2 GC-ARM on-board RAM management algorithm                             | 129 |

| 7.3 Identifying performance anomalies of SSD in enterprise environment . | 130 |

| 7.4 SSD-friendly IO scheduler                                            | 132 |

| Bibliography                                                             | 133 |

# List of Figures

| 1.1 | Overview of SSD design space                                              | 4  |

|-----|---------------------------------------------------------------------------|----|

| 2.1 | Analysis of temporal locality of two workloads                            | 20 |

| 2.2 | An architectural view of the PUD-LRU-based SSD                            | 23 |

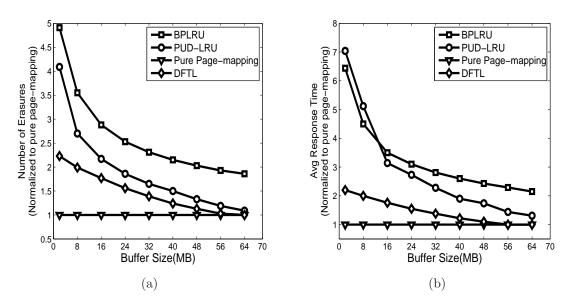

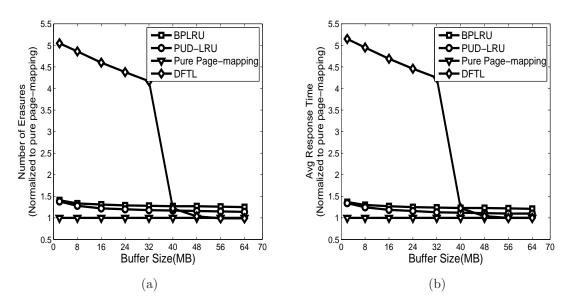

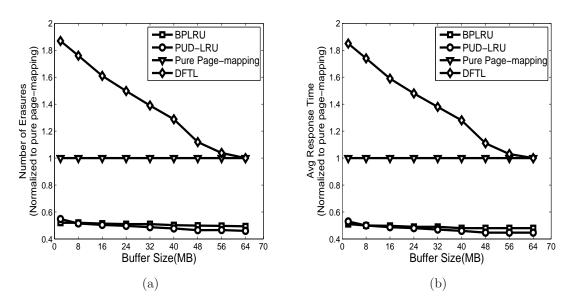

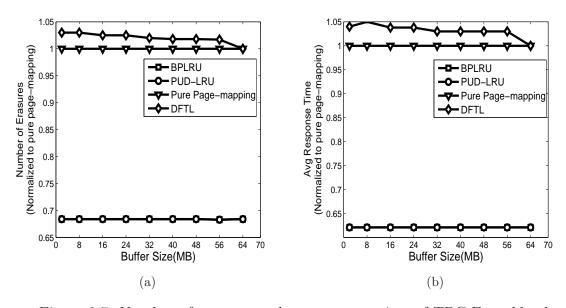

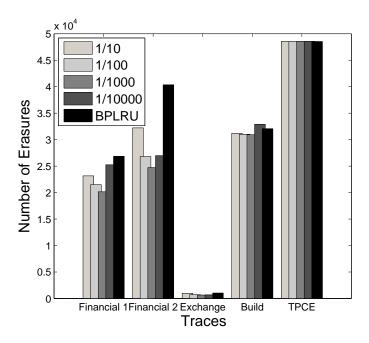

| 2.3 | Number of erasures and avg response time of Financial 1 workload          | 32 |

| 2.4 | Number of erasures and avg response time of Financial 2 workload          | 32 |

| 2.5 | Number of erasures and avg response time of Exchange workload             | 33 |

| 2.6 | Number of erasures and avg response time of Build workload                | 33 |

| 2.7 | Number of erasures and avg response time of TPC-E workload                | 34 |

| 2.8 | Number of erasures and average response time based on different threshold | 36 |

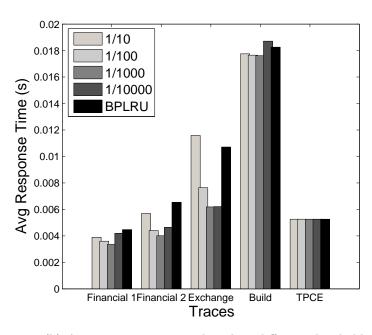

| 2.9 | Destaging efficiency of five workloads                                    | 38 |

| 3.1 | Performance impact of GC efficiency in SSDs                               | 44 |

| 3.2 | Comparison between different destaging policies showing the advantage of  |    |

|     | GC awareness                                                              | 48 |

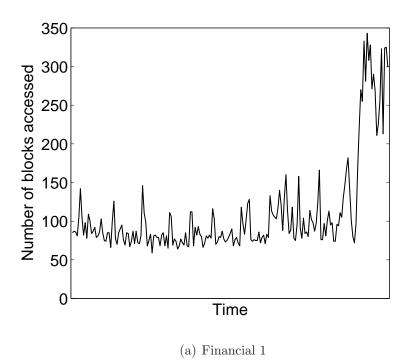

| 3.3 | Number of distinctive blocks accessed per 500 requests                    | 51 |

| 3.4 | Interplay between pages in the write buffer and the mapping entries       | 52 |

| 3.5 | The GC-ARM architecture                                                   | 54 |

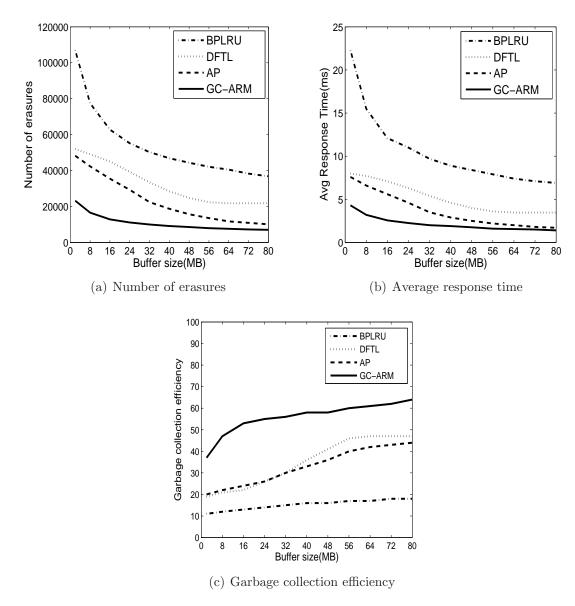

| 3.6 | GC efficiency evaluation of Financial 1 workload                          | 61 |

| 3.7 | GC efficiency evaluation of Financial 2 workload                          | 62 |

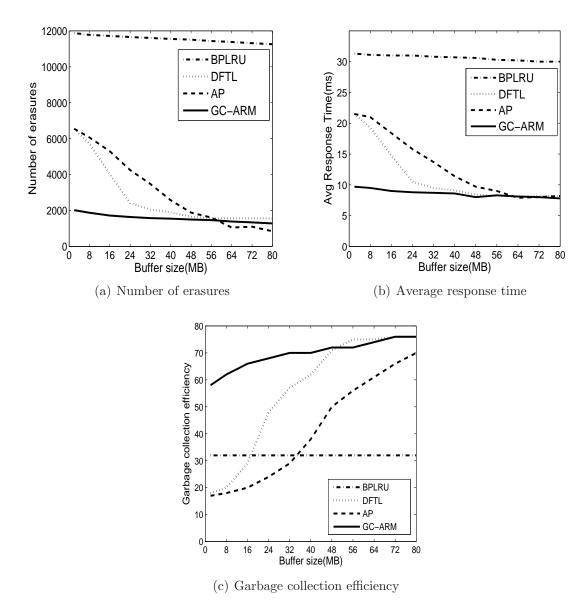

| 3.8  | GC efficiency evaluation of Exchange workload                                 | 63 |

|------|-------------------------------------------------------------------------------|----|

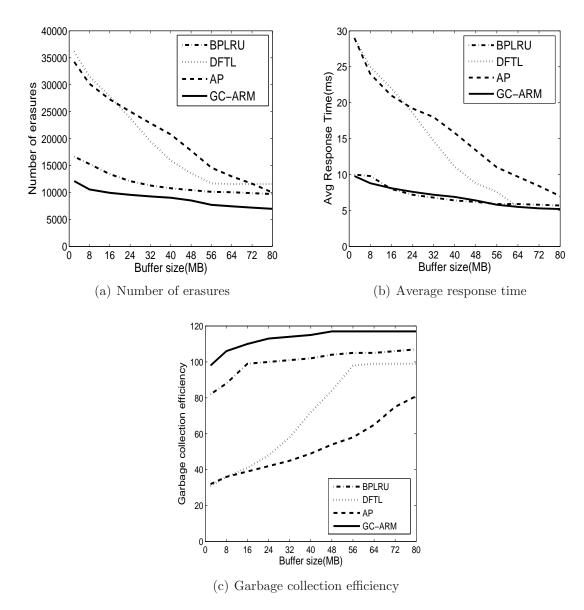

| 3.9  | GC efficiency evaluation of MSN workload                                      | 66 |

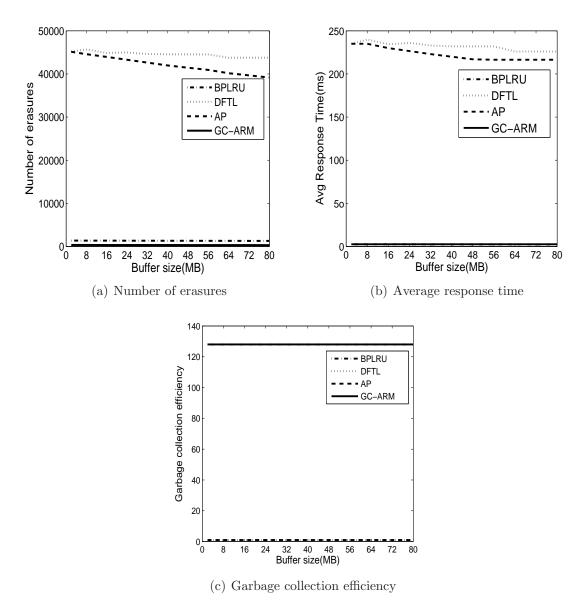

| 3.10 | GC efficiency evaluation of TPC-E workload                                    | 67 |

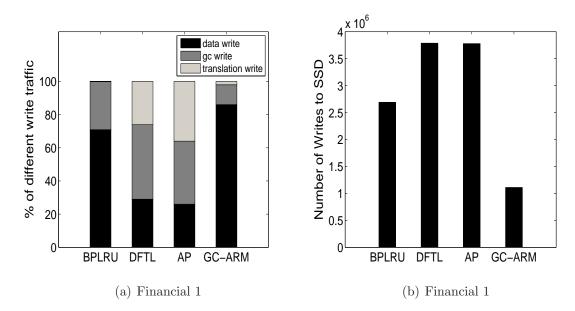

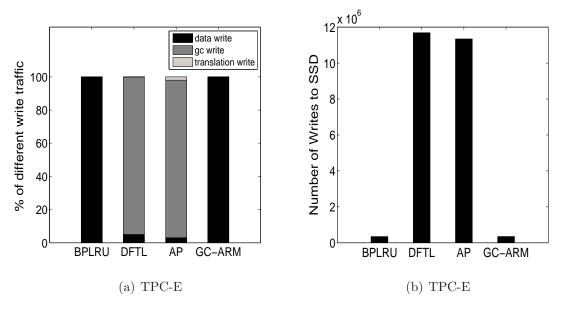

| 3.11 | Write traffic distribution and the total number of writes of Financial $1$ .  | 69 |

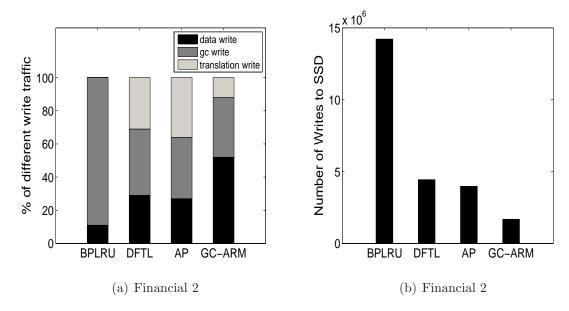

| 3.12 | Write traffic distribution and the total number of writes of Financial $2$ .  | 70 |

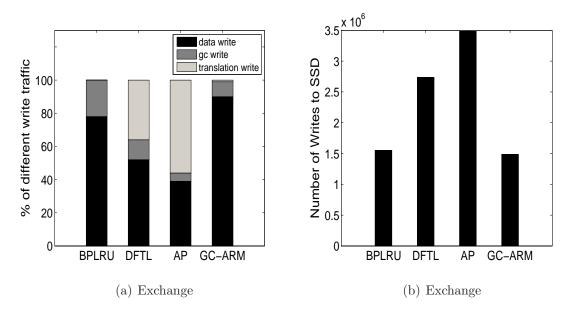

| 3.13 | Write traffic distribution and the total number of writes of Exchange $$ . $$ | 70 |

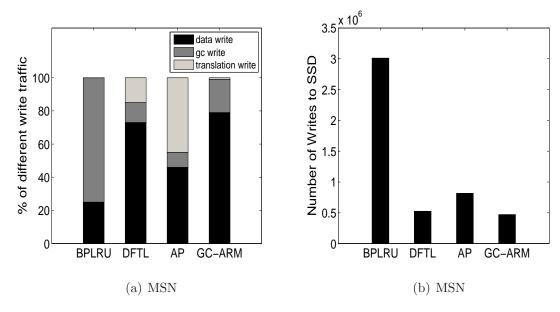

| 3.14 | Write traffic distribution and the total number of writes of MSN              | 71 |

| 3.15 | Write traffic distribution and the total number of writes of TPC-E            | 71 |

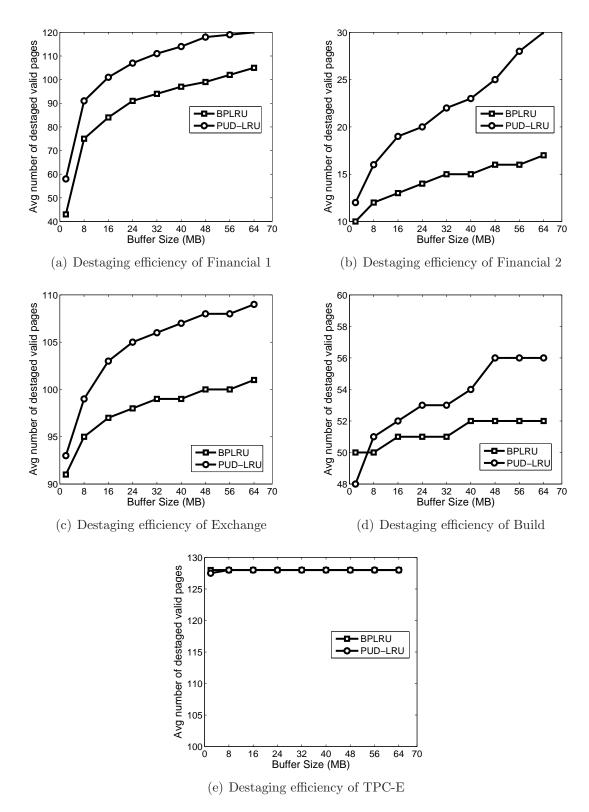

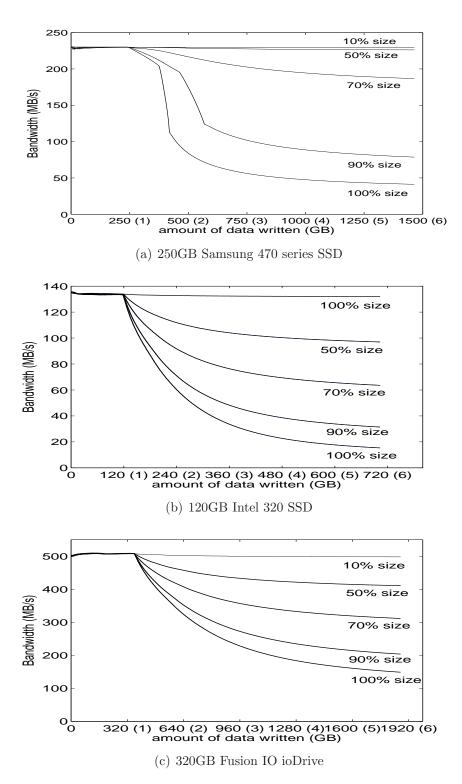

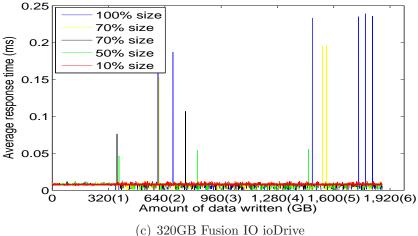

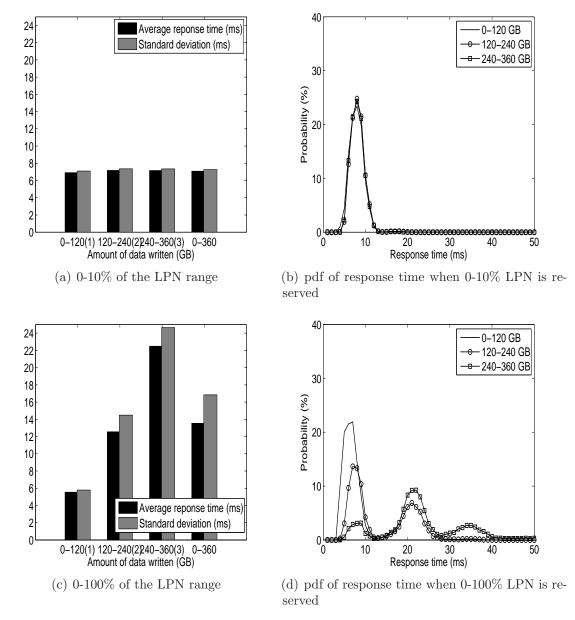

| 4.1  | Performance impact of GC efficiency in SSDs – bandwidth as a function         |    |

|      | of the amount of data written and the percentage of reserved LPN range        | 81 |

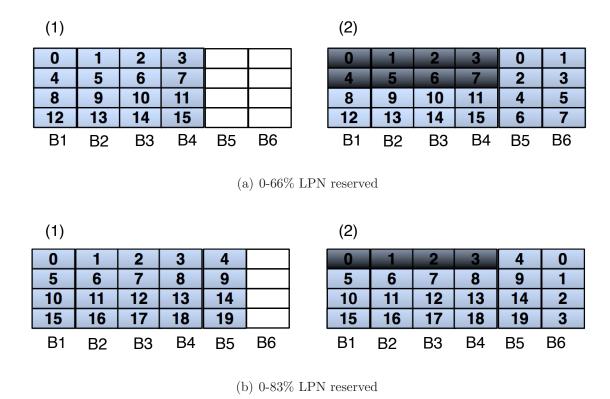

| 4.2  | Examples illustrating GC efficiency when different LPN range is reserved      | 83 |

| 4.3  | Performance impact of GC efficiency in SSDs – write response time as          |    |

|      | a function of the amount of data written and the percentage of reserved       |    |

|      | LPN range                                                                     | 85 |

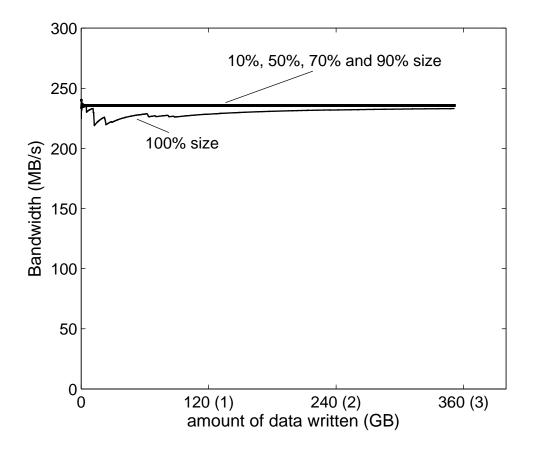

| 4.4  | Impact of mapping policies – bandwidth of 120GB OCZ Vertex 3 SSD as           |    |

|      | a function of the amount of data written and the percentage of reserved       |    |

|      | LPN range                                                                     | 89 |

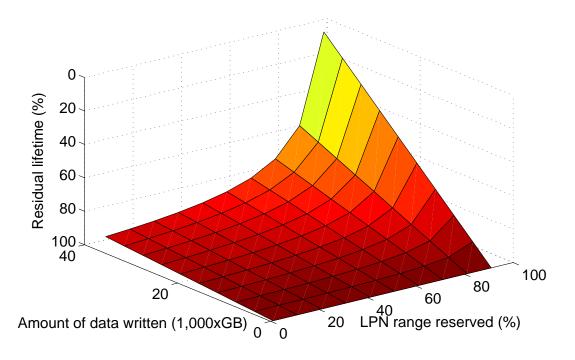

| 4.5  | Residual lifetime as a function of reserved LPN range and the amount of       |    |

|      | data written                                                                  | 92 |

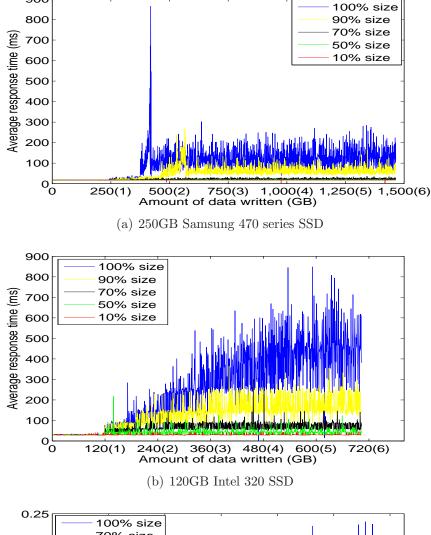

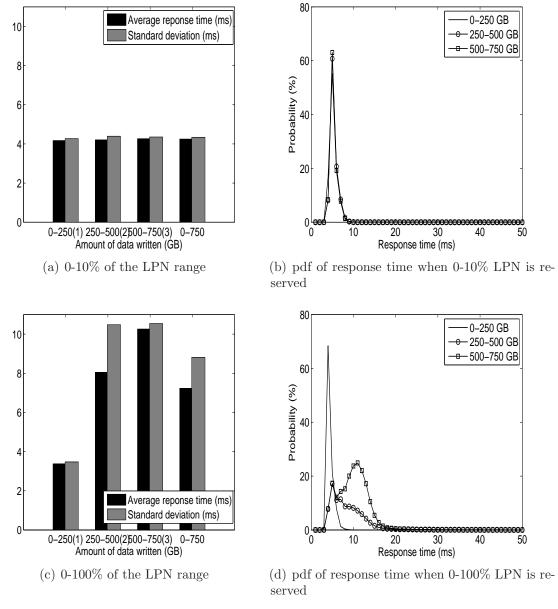

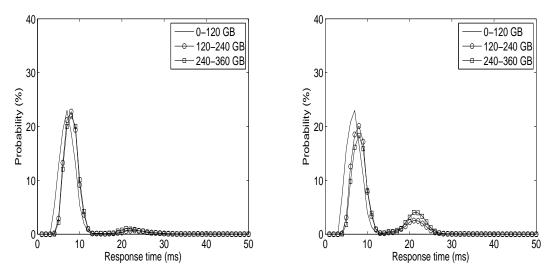

| 4.6  | Average response time, standard deviation and distribution of response        |    |

|      | time of the Samsung 470 Series SSD                                            | 93 |

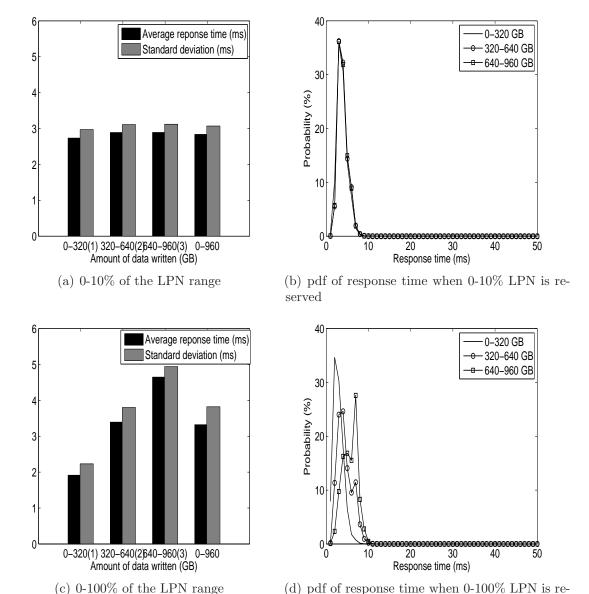

| 4.7  | Average response time, standard deviation and distribution of response        |    |

|      | time of the Intel 320 SSD $\dots$                                             | 94 |

| 4.8  | Average response time, standard deviation and distribution of response        |    |

|      | time of the Fusion IO ioDrive                                                 | 95 |

| 4.9  | Average response time of read requests of Intel 320 SSD at different GC  |      |

|------|--------------------------------------------------------------------------|------|

|      | efficiency                                                               | 98   |

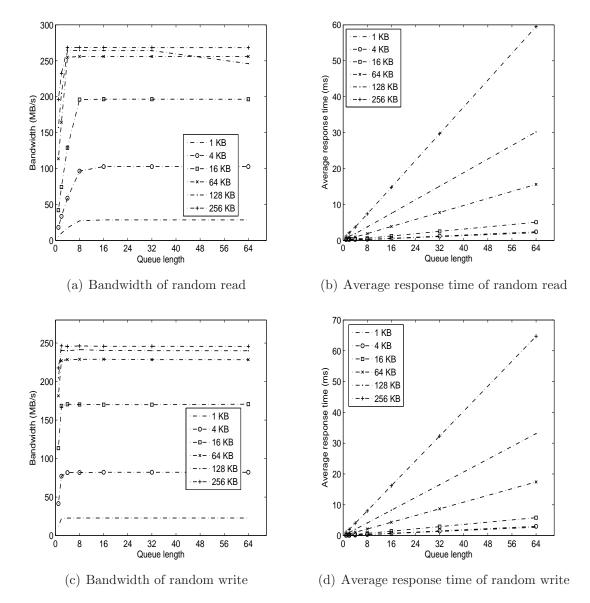

| 4.10 | Tradeoff between bandwidth and average response time of Samsung 470      |      |

|      | SSD                                                                      | 100  |

| 4.11 | Tradeoff between bandwidth and average response time of Intel 320 SSD    | 101  |

| 4.12 | Tradeoff between bandwidth and average response time of Fusion IO ioDriv | e102 |

| 5.1  | Bandwidth as a function of different schedulers and workloads of Fusion  |      |

|      | IO ioDrive                                                               | 111  |

| 5.2  | Bandwidth as a function of different schedulers and workloads of Sandisk |      |

|      | SSD                                                                      | 112  |

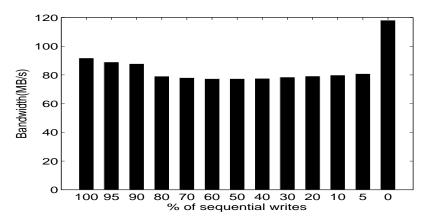

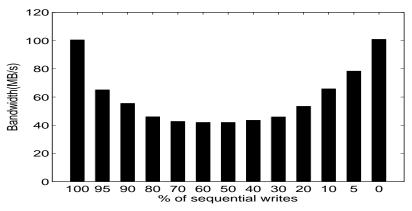

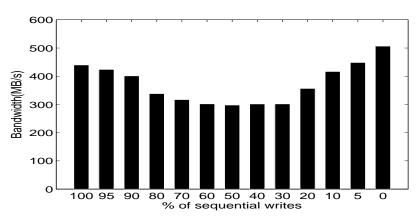

| 5.3  | Impact of mixing read and write requests – bandwidth as a function of    |      |

|      | the percentage of sequential write requests                              | 113  |

| 5.4  | Overall architecture of SSD-friendly IO scheduler                        | 115  |

| 5.5  | Flowchart of the SSD-friendly IO scheduler                               | 119  |

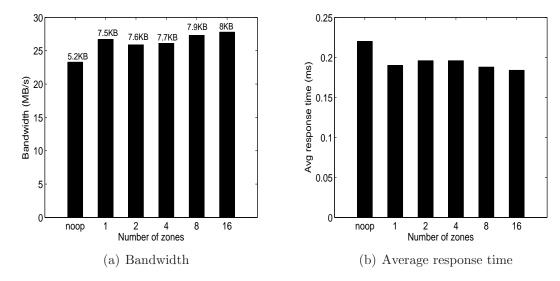

| 5.6  | Bandwidth and average response time as a function of number of zones     |      |

|      | and schedulers for Financial 1 workload                                  | 121  |

| 5.7  | Bandwidth and average response time as a function of number of zones     |      |

|      | and schedulers for Financial 2 workload                                  | 121  |

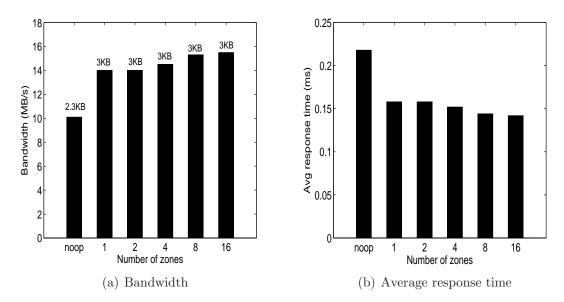

| 5.8  | Bandwidth and average response time as a function of number of zones     |      |

|      | and schedulers for Exchange workload                                     | 122  |

| 5.9  | Bandwidth and average response time as a function of number of zones     |      |

|      | and schedulers for MSN workload                                          | 122  |

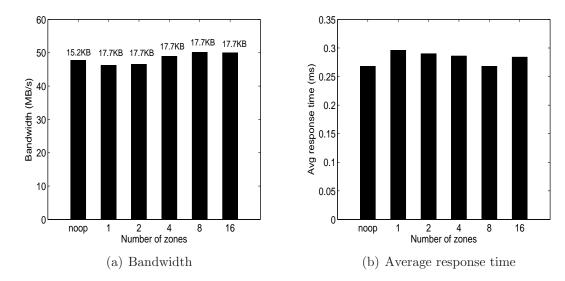

| 5.10 | Bandwidth and average response time as a function of number of zones     |      |

|      | and schedulers for Build workload                                        | 123  |

## List of Tables

| 2.1 | A performance comparison between BPLRU and page-mapping FTL $$ | 18 |

|-----|----------------------------------------------------------------|----|

| 2.2 | I/O characteristics of workloads studied                       | 21 |

| 2.3 | An illustrative comparison between PUD-LRU and BPLRU           | 26 |

| 2.4 | Configuration parameters of SSD                                | 31 |

| 4.1 | Specifications of SSDs                                         | 80 |

## Chapter 1

#### Introduction

NAND Flash memory, in the form of Solid State Drive (SSD), is being increasingly employed in mobile and personal storage systems to improve performance, save energy and increase mobility due to its attractive features such as energy efficiency, good random read performance, strong shock resistance and small form factor, while enterprise-level storage systems and many enterprise applications also employ SSD as a cache device to meet mission-critical requirements [10, 19, 28, 32, 47].

#### 1.1 NAND flash memory SSD characteristics

#### 1.1.1 Characteristics

NAND flash memory consists of a large amount of flash blocks, each of which in turn consists of many fix-sized pages (4KB or 2KB). The access to NAND flash memory is at the granularity of a page. These blocks are called *erase blocks*. Each page inside an erase block can only be written once before the entire block is erased, a NAND flash memory specific requirement known as *erase-before-write* [29]. The value of each target bit in NAND flash can only be programmed from "1" to "0" in a write

operation, but not in the reversed direction. Once a page is written, it must be erased, where all bits are reset to "1", before the next write operation can be performed on the same page. Furthermore, while the write operation can be applied to an individual page, the erase operation can only be applied to an entire block at a time. Moreover, an erase operation is much slower than both a write and read operation. Therefore, many studies try to reduce the number of erasures, delay the erase operations or parallelize them.

When an update (write) request arrives, the targeted pages need to be invalidated and new pages are allocated to store the new content, also known as *out-of-place* update. Because NAND flash memory does not have a moving head as in Hard Drive Disk (HDD), the random read performance is much higher than that of HDD. The high random read performance is one of the best features that system developers rely on to deploy SSD in either enterprise systems or personal computers.

Despite of NAND flash memory SSD's many attractive features, it suffers from the following two physical limitations that restrict the direct deployment of SSD in the enterprise-level systems.

#### 1.1.2 Two physical limitations of SSD

The first restriction comes from the *erase-before-write* and *out-of-place* update characteristics of SSD mentioned above. Over time, after update requests have generated many invalid pages, blocks containing invalid pages must be erased after valid pages in these blocks are copied to other newly allocated blocks, a process often referred to as *Garbage Collection* (GC). The GC process is a read-write-erase operation sequence that first moves the valid pages from the victim block to a free block, then erases the victim block. The GC process affects the performance of SSD significantly not only

because an erase operation takes much more time than a read (e.g., X100) or write (e.g., X10) [41], but also because GC induces significant write amplification [45], i.e., copying valid pages in the victim blocks to other available blocks before they are erased. Due to the time-consuming erase operations and data movement, this GC problem results in poor write performance, especially for a random-write workload, thus negating the advantages of SSD in case of write-intensive workloads. Previous studies [11, 22, 51] have shown that as more and more data is written to SSD, the performance of SSD drops sharply because of the slow erase operations caused by the GC process.

Another limitation of SSD that affects its direct application in an enterprise environment is the endurance problem. The count of erasures per block for the SLC flash memory, where each cell contains a single bit of value, is typically limited to 100,000 while that for the MLC flash memory, where each cell contains 2 bits of value, is limited to only 10,000 or 5,000 [18]. As the density of the NAND flash memory in SSD further increases, the count of erasures of the TLC flash memory, where each cell contains 3 bits of value, is reduced still further. It was reported that SSDs based on the MLC flash in an enterprise environment could easily wear out in 23 days of use [42], which is far too short to be useful.

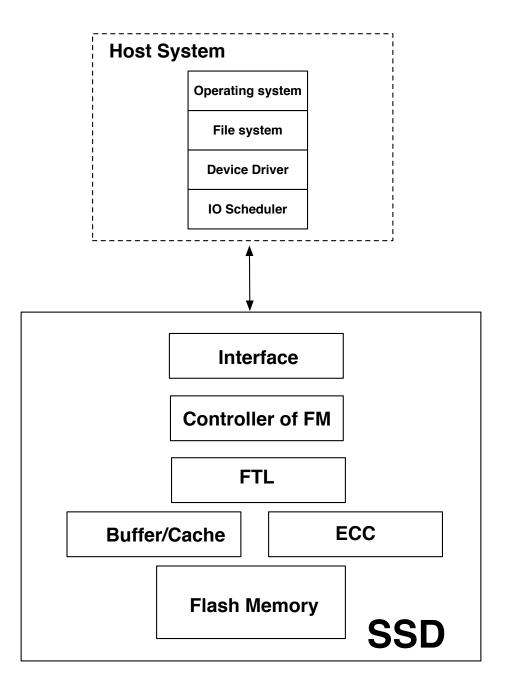

#### 1.2 SSD functional components

Figure 1.1 represents the general functional components and overall design space of SSD. A typical SSD is composed of an interface, a controller in the form of firmware, a Flash Translation Layer (FTL), a write buffer or cache and an error-correction-code functional component. The SSD is connected to the host machine, which has an OS, file system, device driver and IO scheduler from top to bottom. Both the FTL and

Figure 1.1: Overview of SSD design space

write-buffer functional components use the on-board RAM to store mapping entries or buffer data.

#### 1.2.1 Flash translation layer (FTL)

Flash Translation Layer (FTL) is a software layer sitting on top of the physical medium of SSD, and maintains a mapping table in a small RAM in SSD that maps a request's logical page number (LPN) to its physical page number (PPN) to emulate a hard disk drive. Further, by means of intelligent wear-leveling and GC mechanisms, FTL can evenly distribute erasures to flash blocks, achieving the goals of improving the performance and lengthening the lifetime of SSD.

Many studies try to utilize the on-board RAM as an FTL on the FTL design to ease the *erase-before-write* problem [3, 4, 9, 13, 25, 29, 30, 33, 48], by either employing multiple mapping granularities [3, 4, 25, 33] or exploiting the content similarities in the write requests [9].

Page-mapping FTL and block-mapping FTL are two classic FTL algorithms. In a page-mapping FTL [3], a mapping table is used to store and manage the mapping between LPN and PPN. LPN is used as an application-visible data index above the block interface while PPN is used to index the actual data by SSD at the device level. Page-mapping FTL can map an LPN to wherever a PPN is available in SSD and garbage-collect only the erase blocks with invalid pages, thus minimizing the number of erase operations. However, storing the page-mapping table requires a very large memory capacity. With flash memory's continued growth in size, this memory overhead increases dramatically. For example, a 128GB SSD with a page size of 2KB has 2<sup>26</sup> entries in its mapping table. If an entry contains 16 bytes, the page-mapping table will occupy 1GB memory, which is too expensive for the SSD to be cost-effective.

To reduce the space overhead of page-mapping FTL, block-mapping FTL [4] divides a user request's LPN into two parts: a logical block number (LBN) and a page offset within the block, and maps the LBN to any physical block number (PBN) in

SSD. As a result, the block-mapping table size is reduced to  $\frac{1}{N}$  of that of a page-mapping table, where N is the number of pages in each erase block. However, an LPN can only be mapped to a fixed page offset in any physical block. The page offset is calculated as LPN%N. So, it is very likely that two LPNs having the same page offset will conflict, if there is no other block with a free page at the same page offset. In this case, up to two erase operations must be initiated, which adversely affects the performance.

Several hybrid FTL algorithms have been proposed to address the intrinsic problems of page-mapping FTL and block-mapping FTL. Log-block FTL [25], also known as Block Associative Sector Translation (BAST), is a popular FTL algorithm that is widely used in commercial SSD products, which uses multiple blocks as log blocks to log users' writes in flash memory. The block-length sequence of write requests will be first issued to a log block from its first page to its last page sequentially. Once every page in this log block is written, the log block will replace the corresponding data block. This operation is called *switch merge*, in which only one erase operation is required. However, if the log block is not written sequentially from the first page to the last page, a new block is allocated and a full merge operation is initiated, meaning that it will copy the valid pages from the log block and its corresponding data block to the newly allocated data block. Then, the log block and its corresponding data block are erased. In this case, two erase operations are required. Although log-block FTL is more flexible than block-mapping FTL, it suffers from the block thrashing problem [29]. In other words, intensive random writes consume log blocks very rapidly, and thus the FTL has to spend much of its time merging and erasing while postponing processing newly arrived requests, which significantly degrades the performance.

Several improved versions of the original log-block based FTL algorithm have been proposed to exploit temporal locality or sequential locality in the access patterns.

Fully Associative Sector Translation (FAST) [29] allocates the same log block to more than one data block, which increases the utilization of log blocks. However, it suffers from a slow merge problem because the algorithm has to search for more than one data block to execute a full merge. Moreover, it can not handle more than one sequential stream or differentiate a sequential stream from among random requests.

Based on FAST, the Locality-Aware Sector Translation (LAST) [30] scheme employs an access detector to detect whether a request is sequential or random. However, the fact that it simply declares that consecutive requests larger than 4KB are sequential makes it somewhat arbitrary and potentially ineffective.

Demand-based page-level FTL (DFTL) [13] was recently proposed to address the problem caused by the limited number of log blocks in the log-structured FTLs by employing a locality-aware and space-efficient page-level mapping scheme. It reduces the RAM space required to store the page-mapping table by storing only a small subset of the mapping entries in RAM in an LRU queue while leaving the rest in reserved pages in SSD. Mapping entries are stored consecutively based on their logical page numbers (LPNs) in the reserved translation pages in SSD. Translation pages in SSD are further organized into translation blocks. For example, a typical 4KB translation page can store as many as 512 8-Byte logically contiguous mapping entries. Mapping entries in RAM are destaged to translation pages in SSD when the RAM-cashed LRU queue is full and a request miss on this queue causes an entry replacement. Each time an entry from RAM is destaged to a translation page, the latter is invalidated after its old content and the newly destage entry are copied to a newly allocated translation page from the reserved SSD pool for translation blocks, as a result of the out-of-place update property of SSD [13]. When no valid translation pages can be found in the reserved SSD pool for a destaged entry, the garbage collection process is invoked to recycle translation blocks, which results in a significant number of wasteful and harmful

translation erasures that would never happen in a pure page-mapping scheme.

#### 1.2.2 SSD-friendly write buffer

The on-board RAM can be utilized as a write buffer [16,21,23,24,34,43]. As a write buffer, the frequently updated data blocks can be kept in the buffer for as long a time as possible before being destaged to the flash physical medium. As a result, a write buffer can not only help decrease the number of erasures but also offer a better I/O performance since a majority of requests can be serviced at the RAM speed.

BPLRU (Block Padding Least Recently Used) [23] is a recently proposed SSDfriendly write buffer algorithm that aims to improve the random write performance of SSDs. It sits on top of a log-block FTL [25,29] and converts random write requests to sequential ones by first reading the missing pages from flash memory and writing them back to SSD again to fill the "holes", a process known as page padding [24]. However, when the request size of the workloads is small and the LPNs of the write requests are scattered (i.e., non-sequential), BPLRU becomes very inefficient because the padding process increases the traffic by reading pages from SSD and writing them back again. More importantly, the increased write-back traffic increases the write amplification because these writes are artificially created by page-padding, not the original workloads. Although BPLRU outperforms other flash-aware buffer management algorithms such as CFLRU (Clean First LRU) |34| and FAB (Flash Aware Buffer Policy) [21] in minimizing the number of erasures and reducing the average response time, it fails to consider the update frequency of each block in the buffer. This, based on our observations, may be harmful to SSD for some typical enterprise and OLTP workloads. For example, an application that updates a database may frequently write to the same block because several columns of a row in a table are often

updated at the same time and their addresses are adjacent to one another. These addresses are likely located in the same or nearby blocks with high probabilities. In other words, when the database frequently performs update operations, some blocks in the underlying storage device will be far more frequently updated than others. This will likely incur expensive erase operations if the storage device is SSD.

CFLRU (Clean First LRU) [34] is a flash-aware buffer-cache management algorithm. It was proposed to exploit the difference in latency between read and write operations. It considers not only the hit rate but also the replacement cost incurred by selecting a dirty page as the victim. It attempts to choose a clean page as a victim rather than a dirty page by splitting the LRU list into the working region and the clean-first region and evicts clean pages preferentially in the clean-first region until the number of page hits in the working region is preserved at a suitable level. CFLRU was found to be able to reduce the average replacement cost of the LRU algorithm by 26% in the buffer cache. However, this advantage diminishes when only write requests are involved. Thus, it is not useful for enhancing the random write performance of SSDs.

FAB (Flash Aware Buffer Policy) [21] is another flash-aware buffer management algorithm. It groups pages that belong to the same erase block together. These groups are managed in an LRU manner. When any page in a group is accessed, the group is moved to the head of the LRU queue. When destaging becomes necessary, a group that occupies the most space is chosen as a victim. FAB is suitable for mobile devices where workloads are predominantly sequential.

The adaptive partitioning scheme [43] for SSD's DRAM-based cache is the only approach that adjusts the size ratio between memory spaces allocated to the write buffer and the mapping table cache. In this scheme, a ghost buffer and a ghost mapping cache collect data or mapping information destaged by the data buffer and

the mapping cache to predict whether it is beneficial to increase the size of the data buffer and decrease the size of the mapping cache or vice versa. However, this adaptive partitioning scheme treats the FTL as a black box when adjusting the size ratio, thus ignoring the important impact of the interactions among FTL, write buffer, and workload characteristics on the SSD performance. Moreover, the ghost write buffer and ghost mapping table incur non-negligible and potentially significant overhead in maintaining the metadata destaged from the real write buffer and real mapping table.

# 1.3 The SSD design space and the scope of the dissertation

The studies of SSD are categorized into either white-box approaches or black box approaches. The white-box approaches address problems from the inside of SSD. The research topics include FTL design, write buffer design, on-board RAM partition, endurance issues, exploiting internal parallelism and garbage collection problems. The black-box approaches view the SSD as a black-box and optimize its performance externally by identifying its performance properties and anomalies and then scheduling the SSD requests appropriately.

#### 1.3.1 White-box approaches

Many studies in this category focus on the FTL design to ease the *erase-before-write* problem [9, 13, 14, 25, 29, 30, 33, 48, 49], by either employing multiple mapping granularities or exploiting the content similarities among the write requests [9, 14, 49]. Other popular studies involve the management of the on-board RAM inside SSD [16, 21, 23, 24, 34, 43]. The next hot topics focus on the endurance issue of SSDs.

Gokiul Soundararajan et al. [22] use HDD as a cache to increase the sequentiality of workloads and reduce the amount of data being written to the SSD. Simona Boboila et al. [5] use a reverse engineering technique to determine whether the chip or the algorithm is the key factor to determine the endurance of SSD.

In this dissertation, we present two white-box approaches to improving the performance of SSD. The first approach is the design and implementation of an on-board write buffer management algorithm. It effectively reduces the number of erasures through judicious write-buffer management. More specifically, based on our experimental observations that transaction processing and other server workloads have strong temporal locality in the form of highly repetitive updates, an important workload property that the state-of-the-art flash-aware write-buffer management schemes such as BPLRU [23] fail to exploit, we propose a new write-buffer management algorithm, called PUD-aware LRU algorithm (PUD-LRU), based on the Predicted average Update Distance (PUD) as the key block replacement criterion on top of log-block FTL and increase the erase efficiency, PUD-LRU maximizes the number of valid pages in the destaged block in each erase operation.

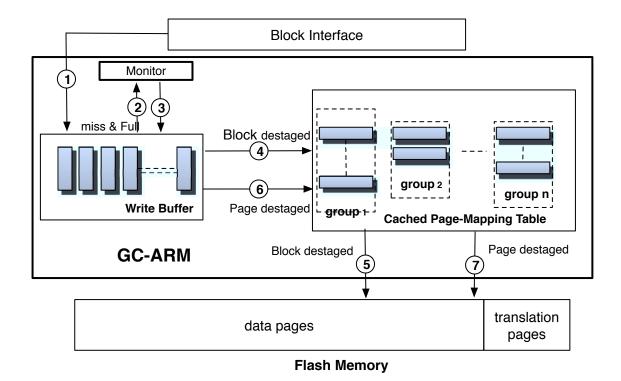

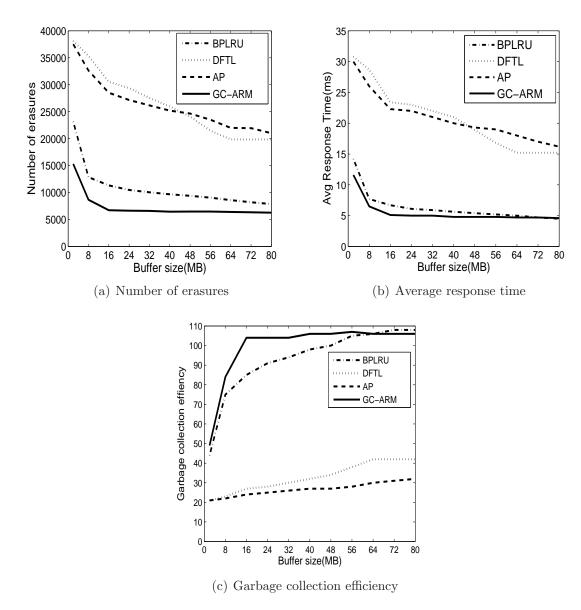

The second approach is an on-board RAM management that exploits the interaction between the write buffer and the FTL. The goal of this approach is to avoid frequent invocation of the garbage collection process. The GC process is slow not only because the erase operation is slow, but also because a great number of pages are copied to other blocks. We propose GC-Aware RAM Management algorithm for SSD, called GC-ARM, which not only improves the GC efficiency to alleviate write amplification, but also cooperates with the FTL to minimize the address translation overhead to reduce the write-back traffic to SSD of the mapping entries. Moreover, GC-ARM can also adjust the size ratio between the write buffer and the FTL in RAM

dynamically based on the workload characteristics.

#### 1.3.2 Black-box approaches

This category of SSD studies treat SSD as a black box to efficiently and effectively deploy SSD in the storage hierarchy and identify the performance anomalies in enterprise environment. These studies also consider whether to deploy SSD as a main storage [27,28], or as a secondary cache above the main storage [22,31]. For example, several emerging enterprise-level products deploy SSD as a cache device and manage it by software [10, 19, 32, 47]. There are other topics in the black-box category that exploit the internal parallelism and identify performance anomalies of SSD [2,7,8,15]. Agrawal Nitin et al. [2] expose the various internal structures and operations that affect the performance of SSD and give possible solutions to users. Feng Chen et al. [7,8] reveal some unanticipated aspects in the performance dynamics of SSD. They also reveal that high-speed data processing benefit from the rich parallelism of the SSD.

In this dissertation, we conduct intensive experiments on a number of commercial SSD products from high-end PCI-E SSD to low-end SATA SSD. Based on the anomalies we identify, we obtain useful insights into SSD performance in enterprise-level environment where workloads tend to be more random and intensive. Based on the findings of the experimental evaluation study, we then provide useful suggestions to designers and developers of enterprise-level applications to make the best use of SSDs and achieve and sustain a near-peak performance while avoiding some of the intrinsic SSD problems.

Based on the parameters we find out, we further design an IO scheduler on top of SSD. We simulate the IO scheduler in the user space by converting workloads into SSD friendly ones. Event-driven evaluation shows that the IO scheduler is effective

in improving SSD performance.

#### 1.4 Contributions of the dissertation

The SSD research topics covered in this dissertation relate to all of the components discussed in the design space. These studies either fall into white-box approaches or black-box approaches. In what follows, we list the key contributions of the dissertation that have advanced the state of the art in SSD design by significantly improving the state-of-the-art approaches in performance and endurance, and revealing and quantifying new SSD properties and performance anomalies.

Revealing the indispensability of write buffer: Our experimental study concludes that a well-designed FTL cannot replace buffer management, which in turn proves that good and novel write-buffer designs on SSD are necessary and indispensable. Based on this conclusion, we design and implement a flash-aware write-buffer management algorithm PUD-LRU that differentiates blocks and judiciously destages blocks based on their update frequency and recency so as to minimize the number of erasures while maximizing the number of valid pages in each erase operation. We find that, based on the experimental results, for sequential traces with very low temporal locality, the pure page-mapping FTL, though flexible, underperforms log-block FTL because of the fact that for such workloads the blocks to be erased contain fewer invalid pages, thus making the garbage collection of the pure page-mapping FTL very inefficient.

Revealing and quantifying the significant performance and endurance impact of low GC efficiency: The GC efficiency is determined by the average number of invalid pages in each victim block to be erased. The more invalid pages there are in an erased victim block, the more free pages the GC process can generate

and the fewer valid pages need to be copied elsewhere, thus achieving the higher GC efficiency. We expose the seriousness of the low-GC-efficiency problem by customizing workloads to change the amount of invalid data in two SSDs when collecting garbage. We show that, when an SSD suffers from low GC efficiency, the SSD write bandwidth can drop to as low as 12% of its peak, which suggests the paramount importance of improving the GC efficiency.

Designing and evaluating GC-aware write buffer management algorithm (GC-ARM): A low GC efficiency implies that more valid pages must be copied from victim blocks to free blocks in the GC process, which constitutes the GC-induced write traffic. To address this problem, GC-ARM dynamically destages either contiguous pages in a block as a whole or a single page from the write buffer based on the benefit the two destaging schemes provide to improve GC efficiency.

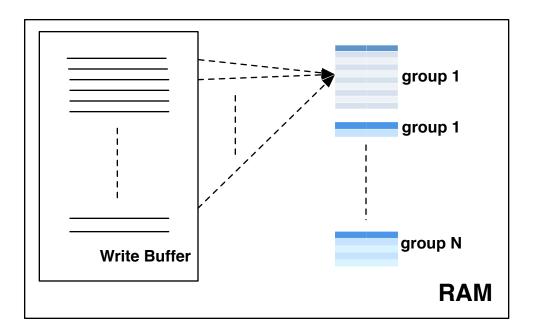

Adaptive and dynamic partition of the RAM between write buffer and FTL mapping table: Based on our experimental observations revealing that the number of distinctive erase blocks accessed for different workloads vary dramatically over time, GC-ARM is designed to dynamically adjust the ratio of the RAM memory space allocated between the write buffer and the cache for the mapping table to further improve the performance of SSD by adapting to the characteristics of workloads.

Minimizing the write-back traffic resulting from mapping-entry replacement in RAM: GC-ARM enables the write buffer to effectively interact with the FTL that groups mapping entries based on the logical page number'(LPN) spatial locality. Based on this design, GC-ARM is able to minimize the write-back traffic induced by victim mapping entries replaced from the cached mapping table and reduce address-translation overhead.

Surmising the FTL mapping policy: In order to improve the GC efficiency by wisely allocating the space of SSD, it is necessary to surmise the mapping policy of a given SSD because different mapping policies have different behavior under writeintensive workloads. Thus, we determine if it is possible to deduce the mapping policy a given SSD employs by examining the responses of the SSD to a given workload.

Estimating the residual lifetime of an SSD: Based on our experimental evaluation results, we develop an analytical model to estimate the residual lifetime of a given SSD. We believe that the model will be useful to the potential users of SSD in the enterprise-level application environment.

Determining whether random read is as fast as believed: The relatively high random-read performance is one of the advantages of SSD. While this is proven to be true in general, we are able to determine whether there are exceptions to the norm, the circumstances under which these exceptions occur, and their implications.

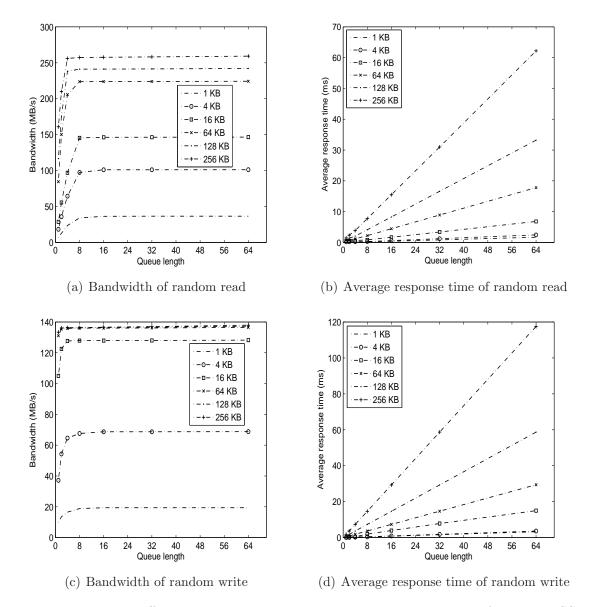

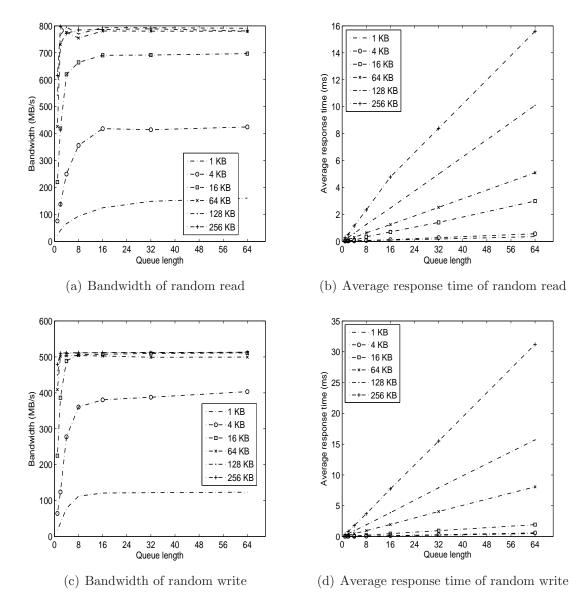

Finding a tradeoff between bandwidth, queue length and average response time: While it is possible to achieve the peak bandwidth by increasing the queue length of requests, we observe that the average response time increases proportionally. We further observe that the average response time is sensitive to the request size. Our investigation based on the experimental evaluation attempts to determine the optimal combination of queue length of requests and request size that achieve the peak bandwidth while minimizing the average response time.

Designing an SSD-friendly IO scheduling algorithm: Based on the parameters we identified in the experiment, we develop an IO scheduling scheme that converts workloads to SSD-friendly ones. Trace-driving experimental results show that it is effective in improving SSD performance.

#### 1.5 Dissertation Organization

This dissertation is organized as follows. In Chapter 2, we introduce PUD-LRU, an SSD-friendly write buffer management algorithm. We first discuss enough background to motivate our work and then give more details about the design and evaluation.

In Chapter 3, we introduce GC-ARM, the on-board RAM management algorithm that focuses on the overall design of buffer, FTL and RAM partitioning between the two. We first give enough background to highlight the importance of the RAM management and then give the detailed design and evaluation of GC-ARM.

In Chapter 4, we evaluate several new SSD products to identify performance anomalies in enterprise environment. Giving the fact that of more and more SSDs are being deployed in enterprise environment, identifying performance anomalies becomes increasingly important. We will explain and analyze based on the experimental results from these SSDs. Further, we give guidelines and suggestions to both SSD vendors and system programmers based on our results.

In Chapter 5, we design and implement an SSD-friendly IO scheduling scheme based on the parameters drawn from Chapter 4. State-of-the-art research of IO scheduling is presented as a background and we evaluate our scheme by trace-driven experiments.

Chapter 6 presents the related work of SSD. We categorize the state-of-the-art related research into several categories.

The dissertation is concluded in Chapter 7 and future work is presented.

## Chapter 2

# Design and Implementation of a Write Buffer Management Algorithm of SSD

The unique SSD feature of erase-before-write imposes a real challenge to the performance and longevity of flash memory SSD. As has been discussed in the Introduction section, there are two general approaches to addressing this challenge at different levels, namely, by means of sophisticated design of address mapping modules in the Flash Translation Layer (FTL) and flash-aware write-buffer management. We find in our experimental study that flash-aware buffer management is necessary and important. Therefore, this chapter focuses on the latter approach to effectively reduce the number of erasures through judicious write-buffer management. More specifically, based on our experimental observations that transaction processing and other server workloads have strong temporal locality in the form of highly repetitive updates, an important workload property that the state-of-the-art flash-aware write-buffer management schemes such as BPLRU [23] fail to exploit, we propose a new write-buffer

Table 2.1: A performance comparison between BPLRU and page-mapping FTL

| Approach         | Number of erasures | Latency (ms) |

|------------------|--------------------|--------------|

| BPLRU            | 22908              | 3.9          |

| Page-mapping FTL | 51373              | 7.9          |

management algorithm, called PUD-aware LRU algorithm (PUD-LRU), based on the Predicted average Update Distance (PUD) as the key block replacement criterion on top of log-block FTL schemes. Moreover, to take advantage of the characteristics of log-block FTLs and increase the erase efficiency, PUD-LRU maximizes the number of valid pages in the destaged block in each erase operation. This work is published in [16].

#### 2.1 Background

Our experimental results show that for some workloads, a well-designed buffer management algorithm that is flash-aware and log-block-FTL-aware can outperform the pure page-mapping FTL, thus showing that the buffer management is necessary and indispensable. Table 2.1 shows the performances of BPLRU on top of the log-block FTL algorithm [25] and the pure page-mapping FTL without any write buffer, running on a 32GB SSD with a page size of 4KB and under the Financial 1 [39] workload. Assuming that each mapping entry is 4 bytes, then the page-mapping FTL requires at least 32MB to store the page-mapping table. On the other hand, we assume 1% of the total SSD blocks in the log-block FTL scheme is reserved as log blocks. So the log-block FTL scheme BAST requires 0.56MB for storing the block-mapping table and the page-mapping information for the log blocks while leaving 31.44MB RAM as the write buffer for BPLRU. The results shown in Table 2.1 suggest to us that designing an efficient buffer management algorithm will be a very worthwhile and

necessary effort that is likely to complement, if not substitute, a good page-mapping FTL scheme.

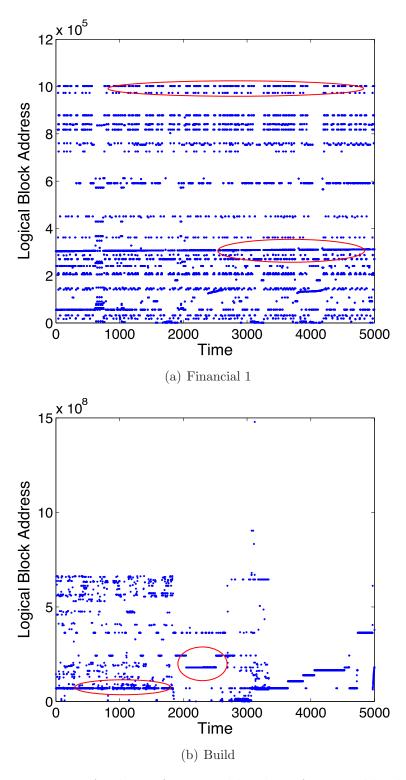

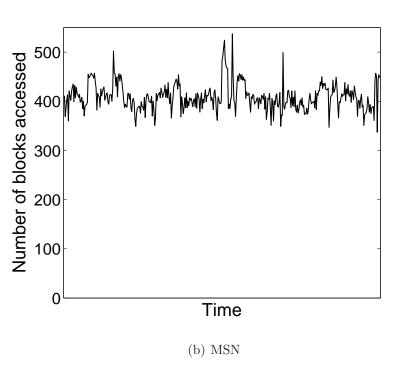

Furthermore, results of our experiments with several representative traces, shown in Figure 2.1(a) and Figure 2.1(b), reveal that some OLTP and server workloads exhibit strong temporal locality. In these figures, each request corresponds to a dot. With only 5,000 requests from the beginning of the traces analyzed, it is amply evident that frequent and repeated update requests are very common in these traces. The ovals in these figures indicate where frequently and repeatedly updated requests take place. We also measured in the experiments how many requests are updated more than once. Table 2.2 shows the characteristics of the five traces that we use in the evaluation section. For the Financial 1 trace, we found that more than 30% of the requested addresses are updated more than once. For the Financial 2 trace, more than 40% of the requested addresses are updated more than once. The Exchange trace also includes a lot of frequently updated requests, where 35% of the requested addresses are updated more than once. The Build trace does not have so many frequent update requests, with only 13% requested addresses being updated more than once. Table 2.2 also indicates that some traces, such as TPC-E, do not exhibit temporal localities. We observe that a large proportion of frequent update operations tend to cluster around small portions of the storage address space in these traces and these addresses are updated extremely frequently. Thus, we believe that, if we can identify frequently updated blocks and buffer them in the write buffer, the number of erasures can be greatly reduced.

We also observe that another factor affecting the number of erasures in SSD is the number of valid pages involved in each destaging operation. For example, if only 32 pages of a 64-page flash erase block are valid and another 32 pages are padded, 32 pages are wasted for this destaging operation. On the other hand, if a data block

Figure 2.1: Analysis of temporal locality of two workloads

Table 2.2: I/O characteristics of workloads studied

| trace            | description               | average request size(KB) | write/read ratio | IOPS | updated more than once |

|------------------|---------------------------|--------------------------|------------------|------|------------------------|

| Financial 1 [39] | an OLTP application       | 3.38                     | 3.31             | 122  | 30%                    |

| Financial 2 [39] | an OLTP application       | 2.38                     | 0.24             | 54   | 40%                    |

| Exchange [36]    | Microsoft exchange server | 12.5                     | 1.53             | 611  | 35%                    |

| Build [36]       | Microsoft build server    | 4.14                     | 41               | 1980 | 13%                    |

| MSN [38]         | MSN storage server        | 22.52                    | 66.7             | 106  | 9%                     |

| TPC-E [37]       | TPC-E benchmark           | 12.75                    | 83.9             | 308  | 1%                     |

with all of its 64 pages being valid is chosen to be destaged, then there is no need to destage another data block.

These important observations, combined with our study of the existing flash-aware buffer management algorithms, motivate us to propose the PUD-LRU algorithm, based on Predicted Average Update Distance (PUD) whose detailed definitions are given in next section. The main idea behind PUD-LRU is to differentiate blocks in the buffer based on their PUD values and judiciously destage blocks in the buffer according to their PUD values so as to minimize the number of erasures while maximizing the number of valid pages in each erase operation. More specifically, PUD-LRU organizes the buffer space into blocks of the erase-block size in the same manner as BPLRU. Furthermore, it divides blocks in the buffer into two groups based on their PUD values. The first group contains blocks with smaller PUD values and thus is defined as Frequently Updated Group (FUG). The second group contains blocks with larger PUD values and thus is defined as Infrequently Updated Group (IUG). When a free block is needed, PUD-LRU chooses a block that contains the most valid pages from IUG to destage, thus destaging as many valid pages as possible while avoiding destaging a block that will be updated soon, which in turn maximizes the efficiency of the destaging operation. The design goal of PUD-LRU is to decrease the number of erasures and thus improve the longevity and performance of SSDs.

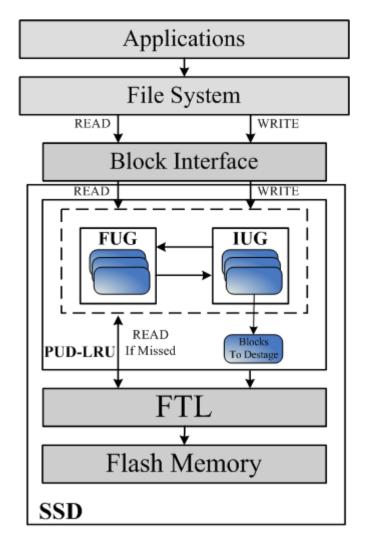

#### 2.2 Design and implementation

As shown in Figure 2.2, a PUD-LRU-based SSD is composed of three main components, namely, the PUD-LRU buffer management module, the Flash Translation Layer (FTL) and the physical flash memory. PUD-LRU sits on top of FTL inside the SSD, monitors and processes the I/O requests issued by the upper file system or database system. Similar to BPLRU, the proposed PUD-LRU is designed on top of a log-block FTL, and uses most of the RAM memory space as a write buffer since the upper storage cache will absorb most of the popular read requests. A very small fraction of the RAM space is used for the block-mapping table and page-mapping for the log blocks. It divides the write buffer into blocks of erase-block size and further groups these blocks into two groups, the frequently updated group FUG and the infrequently updated group IUG as shown in Figure 2.2, based on their PUD values, to be defined later. A read request from the standard block interface is first directed to the PUD-LRU write buffer to search in both groups. If it does not hit, the read request is sent to FTL to be serviced there. Similar to the read request, a write request from the standard block interface is first directed to the PUD-LRU write buffer. If it hits in either of the two groups, the PUD-LRU algorithm will update the metadata in the hit block. On the other hand, if it does not hit in either of the groups and the PUD-LRU write buffer is full, destaging must be performed by choosing a block with the most valid pages from the group whose blocks are not frequently updated, namely, IUG. In order to reduce the number of erasures, PUD-LRU employs the page-padding scheme of BPLRU [24], which reads some pages from the flash memory to pad the block to be destaged as a whole, which reduces the number of erasures by one. The destaging operation makes room for buffering the newly arrived write request that missed at the buffer. If the buffer is not full, a missed write request will be allocated a free

Figure 2.2: An architectural view of the PUD-LRU-based SSD

block in the write buffer and group membership of the newly allocated free block will be determined by its PUD value.

## 2.2.1 Predicted Average Update Distance

Predicted Average Update Distance (PUD) plays a key role in our PUD-LRU algorithm design that leverages the measure of PUD to determine which blocks to keep in or evict from the buffer when the buffer is full and a newly arrived write request

needs a free block to be allocated in the buffer. First, we define the Update Distance (UD) between two update operations to a block as the number of blocks between these two update operations in the update sequence. For example, "ABCDA" represents a sequence of update operations to blocks labeled "A", "B", "C", and "D", and UD between the two consecutive updates to block A is 3. Equation 2.1 formally defines UD of a block. In this equation,  $d_j(i)$  represents the position of block j's ith appearance in the update sequence.

$$UD_{i}(i) = d_{i}(i+1) - d_{i}(i) - 1$$

(2.1)

For example, given an update sequence of "ABXAXAXBXAXXXXB", where "X" represents a block other than block A or B,  $d_A(0)$ ,  $d_A(1)$ ,  $d_A(2)$ , and  $d_A(3)$  are 0, 3, 5, and 9, respectively, and  $d_B(0)$ ,  $d_B(1)$ , and  $d_B(2)$  are 1, 7, and 14, respectively.

To identify the frequently updated blocks, we define average UD, denoted as  $\overline{U_j}$ , in Equation 2.2 below. In this equation, n represents the number of times block j is updated in an update sequence.

$$\overline{UD_j} = \frac{\sum_{i=0}^{n-1} UD_j(i)}{n-1}$$

(2.2)

A small  $\overline{UD}$  of a block implies that the block is frequently updated. Otherwise, it is infrequently updated. For example,  $\overline{UD_A}$  in the above example is 2 and  $\overline{UD_B}$  is 5.5. So block A is updated more frequently than block B, suggesting that block A should not be destaged because updating block A will likely incur more erase operations than B. On the other hand, recency also needs to be taken into consideration in deciding a block's fate in the write buffer. It is possible that a block was updated frequently some time ago and will no longer be updated in the near future. In this case, we

also need to determine when to destage this kind of blocks. Considering the above example again, block A has a higher update frequency but a lower update recency than block B. To take both recency and frequency into consideration, we first define a measure of recency in our algorithm, called Recency Degree (RD), as the number of blocks between the last update operation of a block and the latest update operation of any block. Clearly, similar to the  $\overline{UD}$  measure, the lower the RD value of a block is, the more recently this block has been updated. In other words, a low  $\overline{UD}$  (or RD) value of a block implies a high update frequency (or recency) of this block. For example, RD of block A in the example is 5 while RD of block B is 0, implying that B is more recently updated than A.

To take both of these frequency and recency measures into our consideration, we define the Predicted  $\overline{UD}$  (PUD) of block j as  $PUD_j$ , which is shown in Equation 2.3 that weighs each measure equally.

$$PUD_j = \frac{\overline{UD}_j + RD_j}{2} \tag{2.3}$$

The intuition behind Equation 2.3 is that blocks with small PUD values tend to be updated more frequently within a short and recent period of time, and thus should be kept in the buffer for a longer time than other blocks. On the other hand, blocks that have larger PUD values are either less frequently updated or have a high RD value. Therefore, blocks with larger PUD values should have a higher preference of being destaged.

# 2.2.2 Destaging Efficiency

To minimize the number of erasures, it is important for each destaging operation to involve as many valid pages in one erase block as possible. However, it is possible that

Table 2.3: An illustrative comparison between PUD-LRU and BPLRU

| page writes | BPLRU                   |              | PUD-LRU                                                                                                                 |              |                |

|-------------|-------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------|--------------|----------------|

|             | buffer status           | victim block | buffer status                                                                                                           | victim block | update_counter |

| 0           | [0]                     |              | [0](1,0,0)                                                                                                              |              | 0              |

| 4           | [0], [4]                |              | [0](1,0,0), [4](1,1,0)                                                                                                  |              | 1              |

| 1           | [4], [0,1]              |              | [0,1](2,2,1), [4](1,1,0)                                                                                                |              | 2              |

| 8           | [4], [0,1], [8]         |              | $ \begin{array}{ccc} [0,1](2,2,1), & [4](1,1,0), \\ [8](1,3,0) & \end{array} $                                          |              | 3              |

| 2           | [4], [8], [0,1,2]       |              | [0,1,2](3,4,2), 	 [4](1,1,0),  [8](1,3,0)                                                                               |              | 4              |

| 12          | [4], [8], [0,1,2], [12] |              | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                   |              | 5              |

| 3           | [8], [12], [0,1,2,3]    | [4]          | $ \begin{array}{c c} [4](1,1,0), & [8](1,3,0), \\ [12](1,5,0), & [3](1,6,0) \end{array} $                               | [0,1,2]      | 6              |

| 4           | [12], [0,1,2,3], [4]    | [8]          | [4](2,7,5), [8](1,3,0),  [12](1,5,0), [3](1,6,0)                                                                        |              | 7              |

| 0           | [12], [4], [0,1,2,3]    |              | $ \begin{array}{ c c c } \hline [4](2,7,5), & [8](1,3,0), \\ \hline [12](1,5,0), & [0,3](2,8,1) \\ \hline \end{array} $ |              | 8              |

| 16          | [4], [0,1,2,3], [16]    | [12]         | $ \begin{array}{c cccc} & [4](2,7,5), & [8](1,3,0), \\ & [12](1,5,0), & [0,3](2,8,1), \\ & [16](1,9,0) & \end{array} $  |              | 9              |

| 1           | [4], [16], [0,1,2,3]    |              | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                                                   | [0,3]        | 10             |

| 17          | [16], [0,1,2,3]         | [4]          | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                  |              | 11             |

the block that has the most valid pages will be accessed very soon, so it is necessary to choose blocks that will not be updated soon and have the most valid pages to destage. Therefore, as mentioned earlier, our PUD-LRU scheme divides blocks in the buffer into two separate groups, the Frequently Updated Group (FUG) and the Infrequently Updated Group (IUG). Because blocks in IUG will not be updated soon, the number of valid pages in a block in IUG becomes important. When a free block is needed and the buffer is full, PUD-LRU chooses a block that has the most valid pages from IUG for replacement. More specifically, PUD-LRU first calculates the range of these blocks' PUD values. If the PUD value of a block is within a given threshold, 0.1% in our current simulation study, of the range, the block is considered a member of FUG, otherwise it becomes a member of IUG. The reason for choosing 0.1% as the threshold lies in the fact that only a relatively small portion of the request address space is very frequently accessed [12], as evidenced in our sensitivity study of

PUD-LRU detailed in the evaluation section. As explained in that section, there is no single fixed threshold that will possibly optimize all cases since the optimal threshold value varies with both the workload and the buffer size. By grouping blocks, our PUD-LRU scheme chooses the block that has the most valid pages from IUG with a large PUD value, thus making each destaging operation more efficient.

## 2.2.3 Implementation of PUD-LRU

In order to calculate the PUD value for each block and place the block into either FUG or IUG, PUD-LRU employs three integers to keep track of the update information for each block. The first integer tracks the position where a block was updated the last time. The second integer represents the summation of UD of a block over all updates to this block (i.e., Equation 2.1). The third integer records the number of times a block is updated, which is increased by one each time the block is updated. Our current implementation uses 4B for each of these integers. The space overhead due to these three integers per block, at  $3\times4B=12B$  per 512KB block or 0.002%, is negligible. For each request, the PUD-LRU module executes the PUD-LRU algorithm whose pseudo code is shown in Algorithm 1. In order to calculate the PUD value when necessary, PUD-LRU defines a global variable update\_counter to indicate how many blocks have been updated.  $frequency_i$  denotes the number of times block j is updated.  $last\_update_j$  stores the previous global  $update\_counter$  in block j when block j is updated some time ago. So when block j is updated again, PUD-LRU can calculate the summation of UD of block  $j(UD_i)$  by just increasing  $UD_i$  by the difference between  $last\_update_i$  and the global variable  $update\_counter$ . From Algorithm 1, we can see that PUD-LRU recalculates the PUD value of each block only when a block replacement is required. The time complexity of the algorithm is therefore

#### Algorithm 1 PUD-LRU Algorithm

```

1: Initialize: update\_counter \leftarrow 0

2: Input: Request R with logical block number R_{lba}, request size R_{size} and request

type R_{type}

3: if R_{lba} \equiv read then

4:

offset \leftarrow 0

5:

while offset < R_{size} do

6:

for all blocks, search logical block number R_{lba} + offset

7:

if hit then

return

8:

9:

else

10:

send logical block number R_{lba} + offset to FTL

11:

12:

offset \leftarrow offset + 1

13:

end while

14: else \{/*R_type \equiv write*/\}

15:

offset \leftarrow 0

16:

while offset < R_{size} do

17:

update\_counter \leftarrow update\_counter + 1

18:

for all blocks, search logical block number R_{lba} + offset

19:

if hit block_i then

20:

UD_j \leftarrow UD_j + update\_counter - last\_update_j - 1

21:

frequency_j \leftarrow frequency_j + 1

22:

return

else {/*does not hit any block in the buffer*/}

23:

24:

if need replacement then

25:

size \leftarrow number\_of\_blocks\_in\_the\_buffer

\begin{array}{c} \mathbf{for} \ i \leftarrow 1 \ \mathrm{to} \ \mathrm{size} \ \mathbf{do} \\ PUD_j \leftarrow \frac{update\_counter + UD_j}{frequency_j} \end{array}

26:

27:

28:

end for

29:

PUD\_RANGE \leftarrow get\_pud\_range()

{/*calculate the value range among all blocks in the buffer*/}

30:

for i \leftarrow 1 to size do

if PUD_i < \frac{1}{1000} \times PUD\_RANGE then

31:

32:

group block_i into FUG

33:

else

34:

group block_i into IUG

35:

end if

36:

end for

37:

victim \leftarrow block\_with\_most\_valid\_page()

38:

send block_{victim} to FTL

39:

else {/*the buffer still has space*/}

40:

allocate a new block k

41:

last\_update_k \leftarrow update\_counter

42:

UD_k \leftarrow 0

43:

frequency_k \leftarrow 1

44:

end if

45:

end if

offset \leftarrow offset + 1

46:

47:

end while

48: end if

```

O(n), where n is the number of blocks in the write buffer. Because the buffer size is very limited, n is generally small.

Table 2.3 gives an illustrative example comparing how PUD-LRU and BPLRU process a page-write sequence. In this example, we assume, for simplicity and without loss of generality, that a block contains four pages and the buffer can store 6 pages at most. The page-write request sequence is 0, 4, 1, 8, 2, 12, 3, 4, 0, 16, 1, 17, which corresponds to the block sequence 0, 1, 0, 2, 0, 3, 0, 1, 0, 4, 0, 4. Page numbers are put in square brackets to represent a block. In the case of PUD-LRU, the three variables in the parentheses of a block j indicate the three integers f requency $_j$ ,  $last\_update_j$  and  $UD_j$ , as shown in Algorithm 1, respectively. The last column of Table 2.3 shows the value of the global variable  $update\_counter$ . The three variables are only updated when block j is hit. In this case, f requency $_j$  is increased by one,  $UD_j$  is set to  $update\_counter - last\_update_j - 1 + UD_j(old)$  and  $last\_update_j$  is set to the global  $update\_counter$ .

Because both PUD-LRU and BPLRU employ a page-padding scheme, a destaging operation leads to one erase operation. For BPLRU, four blocks are destaged, which leads to four erase operations. For PUD-LRU, when the *update\_counter* is 6, a destaging operation is initialized. The PUD values for blocks [0,1,2], [4], [8], [12] are 1, 2, 1, 0 respectively. In this example, the threshold is set to  $\frac{1}{100}$ , which groups blocks [0,1,2], [4], [8] to IUG while grouping block [12] to FUG. Block [0,1,2] is chosen as a victim because it contains the most valid pages among the three blocks in IUG. Similarly, when the *update\_counter* is 10, block [0,3] is chosen as the victim because it belongs to the IUG group and contains the most valid pages. PUD-LRU requires two destaging operations in this example scenario, which leads to only two erase operations.

## 2.2.4 Data integrity concern

Data in the write buffer and mapping entries in RAM may be lost if there is a sudden power failure, giving rise the data integrity concern. Several existing technologies can be leveraged to ensure data integrity. For example, SandForce SF1500 [1], which is an enterprise-level SSD product, employs a super-capacitor as an insurance policy to guarantee data integrity. Similar data-integrity protection technologies, such as battery-backed RAM, continuous data protection (CDP), etc., may also be employed.

## 2.3 Performance evaluation

### 2.3.1 Experimental setup

In our trace-driven simulation study of PUD-LRU, we simulate a 32GB SSD, with a page size of 4KB and a block size of 512KB based on FlashSim [53]. FlashSim is an event-driven simulator designed to simulate flash memory SSDs. FlashSim can simulate multiple planes, dies, and packages for parallelism effects. We first extended FlashSim by implementing a log-block FTL [25], which employs 1% of the blocks as log blocks. Then we implemented both the PUD-LRU and BPLRU write-buffer management algorithms on top of the log-block FTL to simulate an SSD integrated with a write buffer. We then implemented DFTL [13] on top of FlashSim that consumes the same resources as those by BPLRU and PUD-LRU. We also implemented the pure page-mapping FTL that stores its entire page-mapping table in the RAM, which requires 64MB RAM space to store its mapping table for a 32GB SSD in our experiment, assuming that each table entry occupies 8-byte RAM space.

Our simulator takes block-level I/O traces as input and generates as output the number of erasures and average response time for a request after the simulation.

OperationLatencyPage read20 usPage write200 usBlock erase1.5 msPage read delay25 usPage write delay200 us

Table 2.4: Configuration parameters of SSD

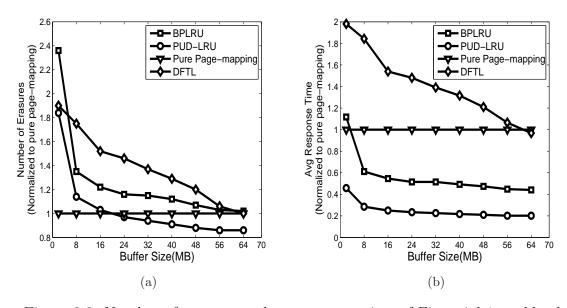

The number of erasures and average response time are used as the endurance and user performance metrics to evaluate the effectiveness of PUD-LRU against BPLRU, DFTL and pure page-mapping FTL.

We fed five traces to the simulator to evaluate and compare the number of erasures and average response time among PUD-LRU, the state-of-the-art write-buffer management algorithm, BPLRU, the sate-of-the-art demand-based page-mapping FTL, DFTL, and the pure page-mapping FTL. The five traces are Financial 1 [39], Financial 2 [39], Microsoft Exchange Server [36], Microsoft Build Server [36], TPC-E benchmark collected at Microsoft [37], whose key I/O characteristics are summarized in Table 2.2. The SSD in our experiment is configured with its key parameters listed in Table 2.4.